FOS standard cell generator from scratch

Jump to navigation

Jump to search

- Speaker: Thomas Kramer <fsic2019 at tkramer dot ch>

Abstract

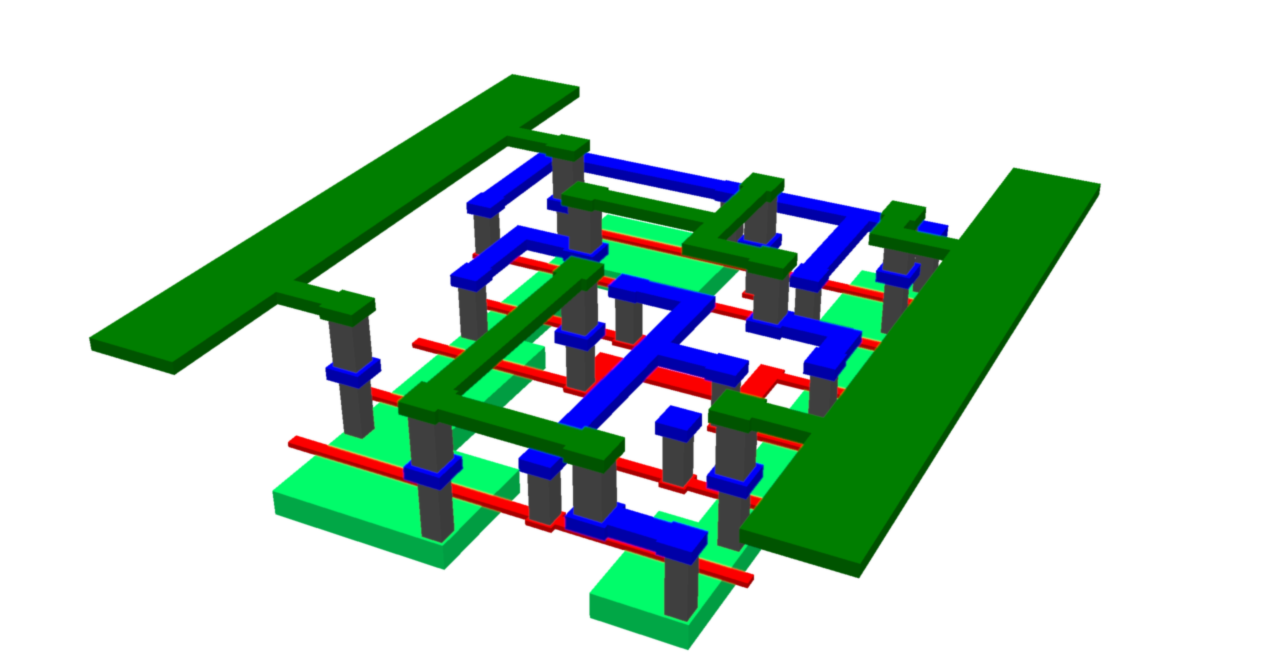

This talk will give an overview of automated standard cell and library synthesis and focus on the experiences made during the ongoing development of a cell generator. The core aspects consist of:

- Place & route inside the cell

- Transistor netlist generation & transistor sizing

- Cell characterization

- Open challenges

Software

General information

- Repository: https://codeberg.org/tok/librecell

- Main documentation website: https://codeberg.org/tok/librecell

- Wikipedia page: TBD

- Wiki page on wiki.f-si.org: TBD

Roadmap

- ✓ Place & route of single row cells

- ✓ Generate GDS

- [in progress] Generate LEF

- ✓ Timing characterization of combinatorial cells

- [in progress] Timing characterization of sequential cells

- Timing characterization of cells with tri-state output

- Timing characterization of cells with asynchronous inputs

- ✓ Generate synthesis liberty file (currently only for combinatorial cells)

- Capacitance extraction using a field solver (maybe FasterCap)

Open challenges

- Netlist synthesis (e.g generate an 'optimal' transistor netlist from a boolean expression)

- Automated transistor sizing

- Routing: Implement router for finer routing pitch to allow more compact cells.

- LEF output: might not be compatible with tools yet. (Pin direction is not yet inferred from the netlist. OBS field ('obstructions') is yet missing).

- Automated LVS check (using KLayout DVB)

- Automated DRC check (using KLayout)

- Capacitance extraction with FasterCap

- Characterization: complete liberty files such that they can be used by synthesizers