Difference between revisions of "FOS standard cell generator from scratch"

Jump to navigation

Jump to search

m (→Roadmap) |

(Add image of standard cell.) |

||

| Line 1: | Line 1: | ||

* Speaker(s): Thomas Kramer | * Speaker(s): Thomas Kramer | ||

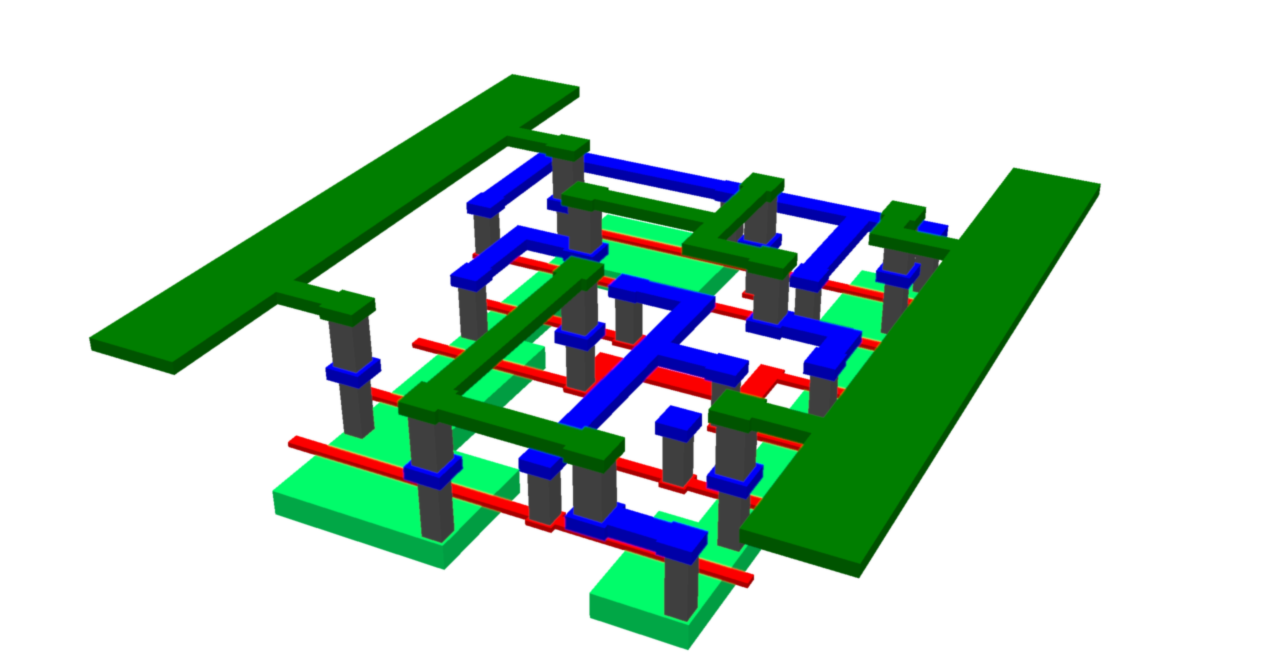

[[File:Latch routed 3d.png|thumb|3D visualization of a 'latch' standard cell.]] | |||

==Abstract== | ==Abstract== | ||

Revision as of 18:20, 4 March 2019

- Speaker(s): Thomas Kramer

Abstract

This talk will give an overview of automated standard cell and library synthesis and focus on the experiences made during the ongoing development of a cell generator. The core aspects consist of:

- Place & route inside the cell

- Transistor netlist generation & transistor sizing

- Cell characterization

Software

General information

- Repository: [not yet published but will come]

- Main documentation website: [not yet published, but will come]

- Wikipedia page: TBD

- Wiki page on wiki.f-si.org: TBD

Roadmap

- ✓ Place & route of single row cells

- ✓ Generate GDS

- [in progress] Generate LEF

- [in progress] Timing characterization of combinatorial cells

- Timing characterization of sequential cells

- Generate synthesis liberty file

- Capacitance extraction using a field solver (maybe FasterCap)