Difference between revisions of "FOS standard cell generator from scratch"

(Add image of standard cell.) |

|||

| (12 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

* Speaker: Thomas Kramer <fsic2019 ''at'' tkramer ''dot'' ch> | |||

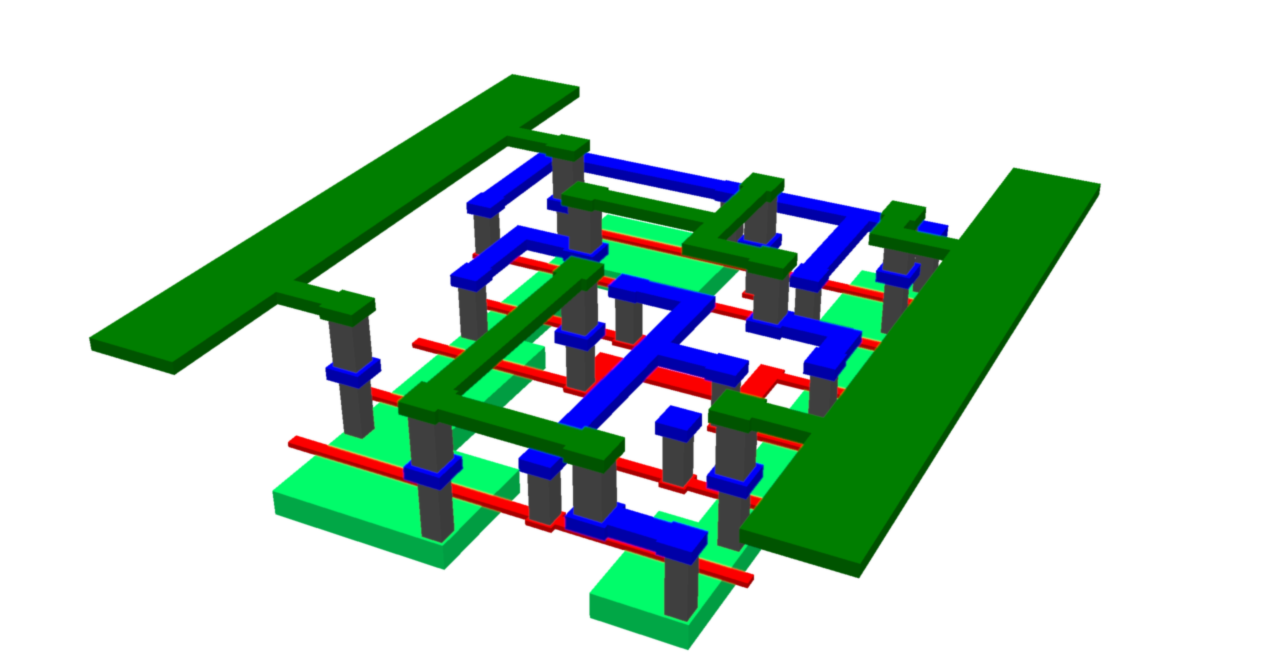

[[File:Latch routed 3d.png|thumb|3D visualization of a 'latch' standard cell. (Made with [https://codeberg.org/tok/gds3xtrude gds3xtrude])]] | |||

* | ==Downloads== | ||

* [[:File:Fsic2019 librecell thomas kramer.pdf|Slides]] | |||

* [https://peertube.f-si.org/videos/watch/b7d22e5a-5138-43ec-953e-cc5565c34ec4 Video recording] | |||

[[File: | ==Abstract== | ||

[[File:Stdcell generation flow.svg|thumb|Flow diagram of standard cell generation flow.]] | |||

Standard-cell based design flows are very common for digital electronics. Usually, standard-cell libraries come with costs and restrictive non-disclosure agreements which are an obstacle for makers, hobbyists and start-ups. NDAs also prohibit collaboration with other groups and make a community driven development very difficult. Having free & open standard-cell libraries would be a partial solution to this problem, but there are many technologies around which require a tailored standard cell library each. Therefore, it would be helpful if standard-cell libraries could be generated from a more abstract description such as a set of netlists and design rules. | |||

This talk introduces [[LibreCell]], a free & open-source standard cell generator which has been developed from scratch in the past few month. | |||

==Software== | ==Software== | ||

===General information=== | ===General information=== | ||

* Repository: | * Repository: https://codeberg.org/tok/librecell | ||

* Main documentation website: | * Main documentation website: https://codeberg.org/tok/librecell | ||

* Wikipedia page: TBD | * Wikipedia page: TBD | ||

* Wiki page on wiki.f-si.org: TBD | * Wiki page on wiki.f-si.org: TBD | ||

| Line 22: | Line 23: | ||

* ✓ Generate GDS | * ✓ Generate GDS | ||

* [in progress] Generate LEF | * [in progress] Generate LEF | ||

* [in progress] Timing characterization of | * ✓ Timing characterization of combinatorial cells | ||

* Timing characterization of | * [in progress] Timing characterization of sequential cells | ||

* Generate synthesis liberty file | * Timing characterization of cells with tri-state output | ||

* Capacitance extraction using a field solver (maybe FasterCap) | * Timing characterization of cells with asynchronous inputs | ||

* ✓ Generate synthesis liberty file (currently only for combinatorial cells) | |||

* Capacitance extraction using a field solver (maybe [https://www.fastfieldsolvers.com/software.htm#fastercap FasterCap]) | |||

== | ==== Open challenges ==== | ||

* Netlist synthesis (e.g generate an 'optimal' transistor netlist from a boolean expression) | |||

* Automated transistor sizing | |||

* Routing: Implement router for finer routing pitch to allow more compact cells. | |||

* LEF output: might not be compatible with tools yet. (Pin direction is not yet inferred from the netlist. OBS field ('obstructions') is yet missing). | |||

* Automated LVS check (using KLayout DVB) | |||

* Automated DRC check (using KLayout) | |||

* Capacitance extraction with [https://www.fastfieldsolvers.com/software.htm#fastercap FasterCap] | |||

* Characterization: complete liberty files such that they can be used by synthesizers | |||

Latest revision as of 17:51, 16 July 2019

- Speaker: Thomas Kramer <fsic2019 at tkramer dot ch>

Downloads

Abstract

Standard-cell based design flows are very common for digital electronics. Usually, standard-cell libraries come with costs and restrictive non-disclosure agreements which are an obstacle for makers, hobbyists and start-ups. NDAs also prohibit collaboration with other groups and make a community driven development very difficult. Having free & open standard-cell libraries would be a partial solution to this problem, but there are many technologies around which require a tailored standard cell library each. Therefore, it would be helpful if standard-cell libraries could be generated from a more abstract description such as a set of netlists and design rules. This talk introduces LibreCell, a free & open-source standard cell generator which has been developed from scratch in the past few month.

Software

General information

- Repository: https://codeberg.org/tok/librecell

- Main documentation website: https://codeberg.org/tok/librecell

- Wikipedia page: TBD

- Wiki page on wiki.f-si.org: TBD

Roadmap

- ✓ Place & route of single row cells

- ✓ Generate GDS

- [in progress] Generate LEF

- ✓ Timing characterization of combinatorial cells

- [in progress] Timing characterization of sequential cells

- Timing characterization of cells with tri-state output

- Timing characterization of cells with asynchronous inputs

- ✓ Generate synthesis liberty file (currently only for combinatorial cells)

- Capacitance extraction using a field solver (maybe FasterCap)

Open challenges

- Netlist synthesis (e.g generate an 'optimal' transistor netlist from a boolean expression)

- Automated transistor sizing

- Routing: Implement router for finer routing pitch to allow more compact cells.

- LEF output: might not be compatible with tools yet. (Pin direction is not yet inferred from the netlist. OBS field ('obstructions') is yet missing).

- Automated LVS check (using KLayout DVB)

- Automated DRC check (using KLayout)

- Capacitance extraction with FasterCap

- Characterization: complete liberty files such that they can be used by synthesizers